100MHz,CPPLC4L-B6-100.0TS,CPPL4,Cardinal正方型钟振,美国进口晶振,Cardinal卡迪纳尔晶振,型号:CPPL4系列,编码为CPPLC4L-B6-100.0TS,电压:3.3V,频率为:100MHz,工作温度范围:0℃至+70℃,频率稳定性:±100ppm,CMOS输出晶振,尺寸为:13.2x13.2x5.6mm金属DIP封装,有源晶振,石英晶振,石英晶体振荡器,时钟振荡器。应用程序:驱动A/D,D/As,FPGAs,数字视频,以太网,GbE,医疗设备,存储区域网络,COTS,宽带接入,SONET/SDH/DWDM,测试和测量。

100MHz,CPPLC4L-B6-100.0TS,CPPL4,Cardinal正方型钟振,产品特点:

•CMOS输出(将与TTL设备接口)

•启用/禁用功能(可选待机功能)

•3.3V或5.0V标称电源电压振荡器

•半DIP封装,工厂编程

100MHz,CPPLC4L-B6-100.0TS,CPPL4,Cardinal正方型钟振,参数表

| Electrical Characteristics CPPL4参数说明 | |||||||

| Parameter | Min | Typ | Max | Unit | Condition | ||

| Frequency Range |

|

100 |

|

MHz | (3.3V : 1-100MHz) | ||

| Frequency Stability | 2 | ±25 | - | ±100 | ppm | For all supply voltages, load changes, aging for 1 year at 25°C ± 2°C, shock, vibration and temperatures. | |

|

|

|

0 | - | 70 |

|

|

|

| Operating Temperature Range options | 2 | -20 | - | 70 | °C | ||

|

|

|

-40 | - | 85 |

|

||

| Supply Voltage1, 2VDD | 2.97 | - | 5.5 | V | See Part Number options on page 2 | ||

| Supply Current IDD(No Load) | - | - | 45 | mA | VDD= 5.0V | ||

| 25 | VDD= 3.3V | ||||||

|

|

|

Cload = 50pF max, VDD= 4.5~5.5V, ≤ 66MHz | |||||

| Output Type | CMOS | Cload = 25pF max, VDD= 4.5~5.5V, > 66MHz | |||||

|

|

|

Cload = 30pF max, VDD= 2.97~3.63V, ≤ 40MHz | |||||

|

|

|

Cload = 15pF max, VDD= 2.97~3.63V, > 40MHz | |||||

|

|

TTL | Cload = 50pF max; VDD= 4.5~5.5V, ≤ 40MHz | |||||

| Duty Cycle | - | - | - | % | See Page 2 | ||

| Output VOH(TTL Level) | 2.4 | - | - | V | VDD= 4.5~5.5V | ||

| (CMOS Level) | VDD- 0.4 |

|

|

V | All voltages | ||

| Output VOL | - | - | 0.4 | V | See Load Circuit and waveform page | ||

| Output TRISEand TFALL | - | - | - | ns | See page 2 | ||

| Startup Time | - | - | 2 | ms | Time for output to reach specified frequency | ||

| VDISABLE | - | - | 0.8 0.2VDD |

|

VDD= 4.5~5.5V | ||

| V | VDD= 2.97~3.63V | ||||||

|

|

VDD= 4.5~5.5V | ||||||

| VENABLE | 2.0 0.7VDD | - |

|

|

VDD= 2.97~3.63V | ||

| Enable Time | - | - | 2 | ms |

|

||

| Disable Time - Pin 1 low to Output Hi-Z |

|

T/2 | T+10 | ns | T = Frequency Period | ||

| - | |||||||

| Disable Current | - | - | - | mA | Enable/Disable: Pad 1 low, output disabled; See above Supply Cur- rent | ||

| - | 0.4 | - | Standby option: Pad 1 low, output disabled, oscillator shutdown | ||||

| RMS Period Jitter | - | 8 | 11 | ps |

|

||

| Period Jitter, Pk-Pk |

|

65 | 99 | ps | >1,000,000 samples | ||

| 65 | 80 | ≤ 33MHz | |||||

|

|

|

> 33MHz | |||||

| Storage Temperature Range | -55 | - | 125 | °C |

|

||

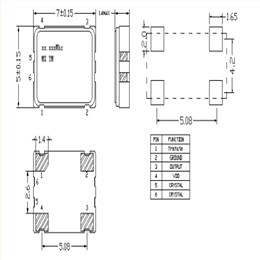

100MHz,CPPLC4L-B6-100.0TS,CPPL4,Cardinal正方型钟振,尺寸图

| 进口晶振 | 品牌 | 系列 | 频率 | Description描述 |

| CPPLC5-A7BR-19.6608PD | Cardinal晶振 | FIPO™ CPPL | 19.6608MHz | OSC XO 19.6608MHZ CMOS SMD |

| CPPLC5-A7BR-25.6TS | Cardinal晶振 | FIPO™ CPPL | 25.6MHz | OSC XO 25.60MHZ CMOS SMD |

| CPPLC5L-A5B6-66.666TS | Cardinal晶振 | FIPO™ CPPL | 66.666MHz | OSC XO 66.666MHZ CMOS SMD |

| CPPLC5L-A5BP-125.0TS | Cardinal晶振 | FIPO™ CPPL | 125MHz | OSC XO 125.000MHZ CMOS SMD |

| CPPLC5L-A7BP-28.9767TS | Cardinal晶振 | FIPO™ CPPL | 28.9767MHz | OSC XO 28.9767MHZ CMOS SMD |

| CPPLC5L-A7BR-100.0TS | Cardinal晶振 | FIPO™ CPPL | 100MHz | OSC XO 100.000MHZ CMOS SMD |

| CPPLC5L-A7BR-27.0TS | Cardinal晶振 | FIPO™ CPPL | 27MHz | OSC XO 27.000MHZ CMOS SMD |

| CPPLC5L-A7BR-34.4064TS | Cardinal晶振 | FIPO™ CPPL | 34.4064MHz | OSC XO 34.4064MHZ CMOS SMD |

| CPPLC5LT-A5B6-120.0TS | Cardinal晶振 | FIPO™ CPPL | 120MHz | OSC XO 120.000MHZ CMOS SMD |

| CPPLC5LZ-A7BP-20.0TS | Cardinal晶振 | FIPO™ CPPL | 20MHz | OSC XO 20.000MHZ CMOS SMD |

| CPPLC5LZ-A7BR-16.0TS | Cardinal晶振 | FIPO™ CPPL | 16MHz | OSC XO 16.000MHZ CMOS SMD |

| CPPLC5-A7BD-27.0TS | Cardinal晶振 | FIPO™ CPPL | 27MHz | OSC XO 27.000MHZ CMOS SMD |

| CPPLC1-B6-24.0TS | Cardinal晶振 | FIPO™ CPPL | 24MHz | OSC XO 24.000MHZ CMOS PC PIN |

| CPPLC1-BP-155.52PD | Cardinal晶振 | FIPO™ CPPL | 155.52MHz | OSC XO 155.52MHZ CMOS PC PIN |

| CPPLC1L-A5BR-13.56TS | Cardinal晶振 | FIPO™ CPPL | 13.56MHz | OSC XO 13.56MHZ CMOS PC PIN |

| CPPLC4-B6-16.896TS | Cardinal晶振 | FIPO™ CPPL | 16.896MHz | OSC XO 16.896MHZ CMOS PC PIN |

| CPPLC4-B6-3.6864TS | Cardinal晶振 | FIPO™ CPPL | 3.6864MHz | OSC XO 3.6864MHZ CMOS PC PIN |

| CPPLC4L-B6-100.0TS | Cardinal晶振 | FIPO™ CPPL | 100MHz | OSC XO 100.000MHZ CMOS PC PIN |

| CPPLC4L-BR-37.5TS | Cardinal晶振 | FIPO™ CPPL | 37.5MHz | OSC XO 37.50MHZ CMOS PC PIN |

| CPPLC4T-A7BR-10.6656TS | Cardinal晶振 | FIPO™ CPPL | 10.6656MHz | OSC XO 10.6656MHZ CMOS PC PIN |

FT5HNBPK16.0-T1,超薄晶振,FOX进口晶振,四脚晶振

FT5HNBPK16.0-T1,超薄晶振,FOX进口晶振,四脚晶振 FY7HCJE12.288-T1,有源晶振,FOX电压晶振,晶体振荡器

FY7HCJE12.288-T1,有源晶振,FOX电压晶振,晶体振荡器 C3290-10.000,瑞斯克电子,5V晶振,石英晶振

C3290-10.000,瑞斯克电子,5V晶振,石英晶振 QTCC230LD12-50.000MHz晶振,Q-TECH晶振,石英贴片晶体,进口晶振

QTCC230LD12-50.000MHz晶振,Q-TECH晶振,石英贴片晶体,进口晶振 Macrobizes晶振,石英振荡器,OS75-3-6-24M-B50-1-TR晶振,四脚贴片晶体

Macrobizes晶振,石英振荡器,OS75-3-6-24M-B50-1-TR晶振,四脚贴片晶体