本应用笔记主要介绍了将32.768K晶振连接到实时时钟(RTC)的晶体选择和布局技术.它还提供有关振荡器电路设计标准,系统设计和制造问题的信息.

振荡器基础知识

振荡器是皮尔斯型振荡器的CMOS反相器变体.图1显示了一般配置.这些RTC包括集成负载电容(CL1和CL2)和偏置电阻.皮尔斯振荡器利用以并联谐振模式工作的晶体.并联谐振模式中使用的晶体被指定为具有特定负载电容的特定频率.为使振荡器以正确的频率运行,振荡器电路必须使用正确的容性负载加载晶振.

图1.带内部负载电容和偏置电阻的RTC振荡器.

准确性

基于晶体的石英晶体振荡器电路的频率精度主要取决于晶体的精度和晶体与振荡器电容性负载之间匹配的精度.如果容性负载小于晶体设计的容量,则振荡器运行速度很快.如果容性负载大于晶体设计的容量,则振荡器运行缓慢.

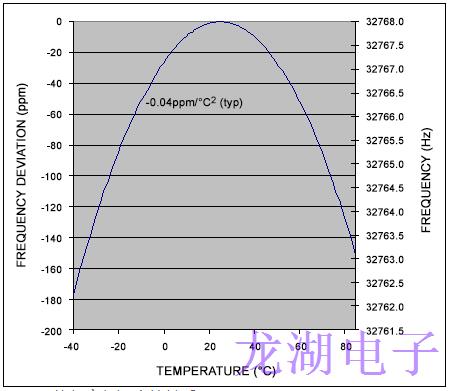

除了晶体和负载匹配的误差之外,随着环境温度的变化,晶体的基频也会发生变化.使用32.768K音叉晶体,它在温度范围内出现误差,如图2所示.误差为20ppm相当于每月约1分钟.

图2.晶体频率与温度的关系.

注意:如果需要更高的精度,可以使用诸如DS32kHz的TCXO晶振.

水晶参数

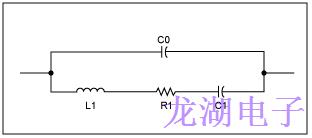

图3显示了晶体的等效电路.在谐振频率附近,电路由包括运动电感L1,运动电阻R1和运动电容C1的串联电路组成.并联分量CO是晶体的并联电容.

图3.晶体等效电路.

负载电容CL是从石英晶振的引脚看到的振荡电路的容性负载.图4显示了CL作为与晶体平行的电容.振荡器电路中使用的负载电容CL1和CL2加上电路中的任何杂散电容组合在一起,形成总负载电容.所有均集成了CL1和CL2电容.应注意尽量减少印刷电路板(PCB)布局中的杂散电容.以下公式显示了CL和负载电容值之间的关系:

CL=[(CL1×CL2)/(CL1+CL2)+CSTRAY]

图4.晶体负载电容和等效并联负载.

大多数晶体允许的最大驱动电平为1μW.所有RTC均低于1μW.可以使用以下公式确定驱动器级别:

P=2R1×[π×32,768(Cò+C大号)VRMS]²

其中VRMS是晶体两端电压的RMS值.

表1.晶体规格

| 参数 | 符号 | 敏 | 典型 | 马克斯 | 单位 |

| 标称频率 | f O. | 32.768 | 千赫 | ||

| 频率容差 | delta f / f O. | ±20 | PPM | ||

| 负载电容 | C L | 6 | pF | ||

| 温度转换点 | T 0 | 20 | 25 | 30 | ℃ |

| 抛物线曲率常数 | ? | 0.042 | PPM /℃ | ||

| 品质因素 | Q | 40000 | 70000 | ||

| 串联电阻 | ESR | 45 | 千欧 | ||

| 分流电容 | C 0 | 1.1 | 1.8 | pF | |

| 电容比 | C 0 / C 1 | 430 | 600 | ||

| 驾驶级别 | D L | 1 | μW |

注1:某些器件允许更高的ESR值,请查看数据表以了解具体要求.

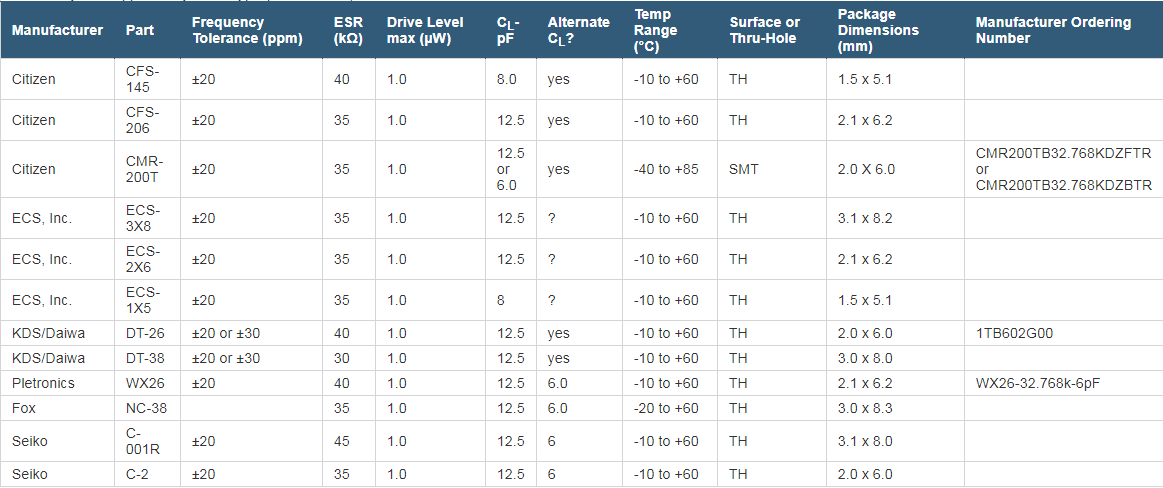

表2.晶体供应商,圆柱型(ESR=45kΩ)

注意:气缸型尺寸为机筒直径和长度,并排除导线.所有尺寸近似.

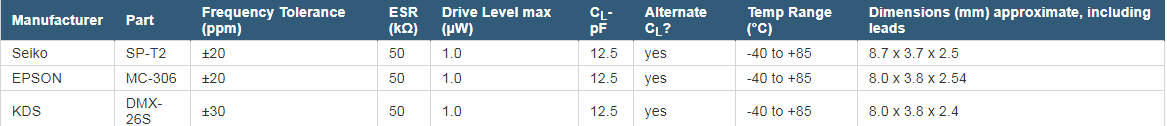

表3.晶体供应商,表面贴装

振荡器启动时间

振荡器启动时间高度依赖于晶体特性,PCB泄漏和布局.高ESR和过大的容性负载是启动时间长的主要原因.使用具有推荐特性和适当布局的32.768K晶振的电路通常在一秒钟内开始.